隨著半導體技術的飛速發展,數字集成電路設計已成為推動信息產業進步的核心力量。合創資本劉華瑞指出,在數字集成電路領域,設計者需重點關注以下幾個方面:

一、功耗與能效優化

在移動設備和物聯網應用普及的背景下,低功耗設計成為數字集成電路的首要考量。通過時鐘門控、電源門控、多電壓域等技術,有效降低動態與靜態功耗,提升芯片能效比。

二、性能與時序收斂

隨著工藝節點不斷縮小,時序收斂面臨更大挑戰。設計者需采用先進的靜態時序分析方法和約束設計,確保電路在目標頻率下穩定工作,同時優化關鍵路徑延遲。

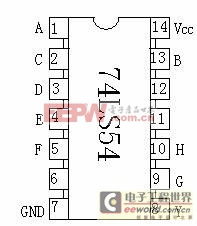

三、可測性設計(DFT)

為提高芯片量產良率,必須內置掃描鏈、存儲器BIST等可測性結構。這不僅能提升測試覆蓋率,還能顯著降低后期測試成本。

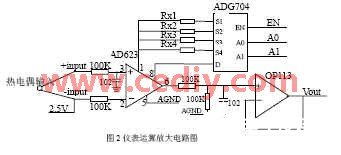

四、系統級驗證

現代數字芯片規模龐大,需要建立完善的驗證環境,采用形式驗證、硬件仿真等方法,確保設計功能正確性,避免流片后出現致命錯誤。

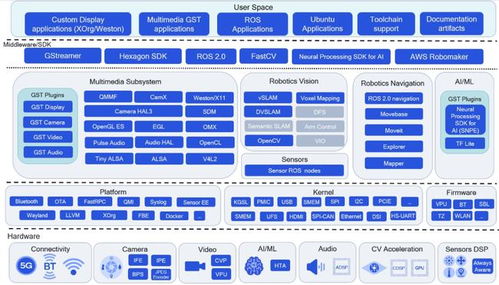

五、IP核復用與集成

基于成熟IP核進行設計復用,可大幅縮短開發周期。但需注意接口標準化、功能驗證等關鍵環節,確保IP集成后的系統可靠性。

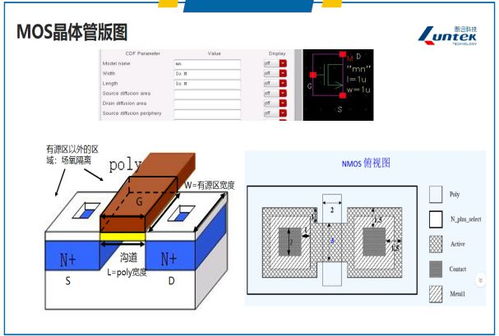

六、先進工藝適配

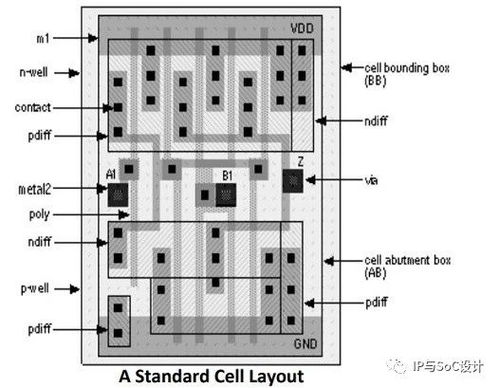

進入納米級工藝后,設計者需應對寄生效應、工藝變異等新挑戰,需要與晶圓廠緊密合作,進行工藝設計套件(PDK)的精準建模和仿真。

劉華瑞強調,數字集成電路設計已進入系統級、智能化的新階段,設計者需要具備跨學科知識,在技術創新與商業化應用之間找到最佳平衡點。只有把握這些關鍵關注點,才能在激烈的市場競爭中占據先機。