在模擬CMOS集成電路設(shè)計(jì)中,頻率響應(yīng)和穩(wěn)定性是放大器設(shè)計(jì)的核心考量因素之一。虛零點(diǎn)法作為一種有效的補(bǔ)償技術(shù),通過在頻率響應(yīng)中引入虛擬的零點(diǎn),改善相位裕度并確保電路穩(wěn)定工作。本文將探討虛零點(diǎn)法的基本原理,及其在計(jì)算機(jī)輔助設(shè)計(jì)中的仿真實(shí)現(xiàn)。

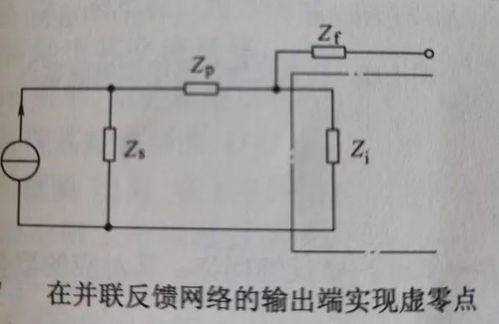

虛零點(diǎn)法的核心思想是在傳遞函數(shù)中構(gòu)造一個(gè)位于高頻區(qū)域的零點(diǎn),以抵消由主極點(diǎn)引起的相位滯后。在兩級運(yùn)算放大器中,密勒補(bǔ)償技術(shù)會引入一個(gè)右半平面零點(diǎn),惡化相位裕度。虛零點(diǎn)法通過增加一個(gè)串聯(lián)電阻與補(bǔ)償電容,將這個(gè)零點(diǎn)移動(dòng)到左半平面或高頻區(qū)域,甚至完全消除其負(fù)面影響,從而提升穩(wěn)定性。

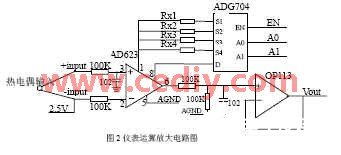

計(jì)算機(jī)仿真在虛零點(diǎn)法的應(yīng)用中扮演著至關(guān)重要的角色。設(shè)計(jì)者可以利用SPICE類仿真工具(如Cadence Virtuoso、HSPICE或LTspice)進(jìn)行頻域分析,觀察補(bǔ)償前后的幅頻與相頻特性。通過參數(shù)掃描優(yōu)化電阻和電容值,可以精確控制零點(diǎn)的位置,實(shí)現(xiàn)最佳的相位裕度。蒙特卡洛分析和工藝角仿真能夠評估工藝偏差對虛零點(diǎn)法效果的影響,確保設(shè)計(jì)的魯棒性。

虛零點(diǎn)法是模擬CMOS集成電路設(shè)計(jì)中優(yōu)化穩(wěn)定性的有效手段,而計(jì)算機(jī)仿真技術(shù)則為其實(shí)驗(yàn)驗(yàn)證和參數(shù)優(yōu)化提供了高效平臺,助力設(shè)計(jì)者實(shí)現(xiàn)高性能、高穩(wěn)定性的模擬電路。