跨界融合新篇章 工博會解碼智能制造,制造業(yè)+互聯(lián)網(wǎng)+IT共創(chuàng)未來——聚焦上海沙龍與云計算裝備技術(shù)服務(wù)

在全球工業(yè)轉(zhuǎn)型升級的浪潮中,智能制造已成為驅(qū)動制造業(yè)高質(zhì)量發(fā)展的核心引擎。在備受矚目的工博會上,谷歌、霍尼韋爾等行業(yè)巨頭齊聚一堂,共同為智能制造的跨界融合路徑答疑解惑。這一進(jìn)程,實質(zhì)上是制造業(yè)、互聯(lián)網(wǎng)與IT技術(shù)深度融合的生動體現(xiàn),而以上海站的專題沙龍及云計算裝備技術(shù)服務(wù)為代表的實踐探索,正為這場轉(zhuǎn)型注入源源不斷的動力。

一、跨界融合:制造業(yè)的必然選擇

傳統(tǒng)的制造業(yè)模式正面臨效率瓶頸與創(chuàng)新挑戰(zhàn)。單純依靠硬件升級或流程優(yōu)化已難以滿足個性化、柔性化與智能化的市場需求。因此,將制造業(yè)的深厚積淀與互聯(lián)網(wǎng)的連通性、IT技術(shù)的數(shù)據(jù)處理能力相結(jié)合,成為突破困局的關(guān)鍵。谷歌憑借其在大數(shù)據(jù)、人工智能及云平臺方面的領(lǐng)先優(yōu)勢,為制造企業(yè)提供了從預(yù)測性維護(hù)到智能供應(yīng)鏈的解決方案;而霍尼韋爾則以其在工業(yè)自動化與控制領(lǐng)域的百年經(jīng)驗,將物理制造過程與數(shù)字技術(shù)無縫銜接。兩者的合作與分享,在工博會上清晰勾勒出“制造業(yè)+互聯(lián)網(wǎng)+IT”三位一體的轉(zhuǎn)型藍(lán)圖。

二、上海沙龍:思想碰撞與實踐交流的平臺

作為中國制造業(yè)的高地與科技創(chuàng)新中心,上海自然成為探討智能制造前沿的焦點。在此舉辦的專題沙龍,不僅匯聚了來自谷歌、霍尼韋爾的技術(shù)專家,還吸引了眾多制造企業(yè)代表、行業(yè)分析師及學(xué)者。沙龍圍繞“智能制造轉(zhuǎn)型中的跨界協(xié)同”展開深度對話:如何利用云計算打破數(shù)據(jù)孤島?IT系統(tǒng)如何與OT(運營技術(shù))安全融合?互聯(lián)網(wǎng)思維怎樣重塑生產(chǎn)組織方式?這些討論不僅解開了許多企業(yè)在轉(zhuǎn)型初期的困惑,更催生了具體的合作意向與試點項目,體現(xiàn)了上海在推動產(chǎn)業(yè)融合方面的樞紐作用。

三、云計算裝備技術(shù)服務(wù):賦能落地的技術(shù)基石

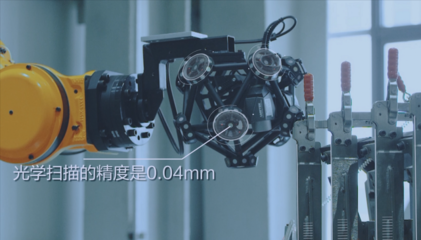

理論探討的落地,離不開堅實的技術(shù)支撐。云計算裝備技術(shù)服務(wù)正是實現(xiàn)智能制造的重要基石。通過將高性能計算、存儲及分析能力以服務(wù)形式提供,企業(yè)無需巨額前期投入即可部署先進(jìn)的制造執(zhí)行系統(tǒng)(MES)、數(shù)字孿生或AI質(zhì)檢平臺。例如,基于云的工業(yè)物聯(lián)網(wǎng)平臺能實時采集設(shè)備數(shù)據(jù),通過算法優(yōu)化生產(chǎn)參數(shù);而裝備的遠(yuǎn)程監(jiān)控與預(yù)測性維護(hù)服務(wù),則大幅降低了停機風(fēng)險與運維成本。這種“服務(wù)化”模式降低了轉(zhuǎn)型門檻,尤其助力中小制造企業(yè)快速融入智能生態(tài)。

四、展望未來:持續(xù)創(chuàng)新與生態(tài)共建

智能制造跨界融合的道路并非一蹴而就,它需要持續(xù)的技術(shù)迭代、人才培養(yǎng)與標(biāo)準(zhǔn)制定。谷歌與霍尼韋爾在工博會上的展示表明,未來的工廠將是物理世界與數(shù)字世界高度同步的“智能體”,其中數(shù)據(jù)成為新生產(chǎn)要素,而云計算與AI則是核心處理工具。上海及長三角地區(qū)憑借其完善的產(chǎn)業(yè)鏈、活躍的資本與政策支持,有望率先形成智能制造創(chuàng)新集群。

從工博會的宏觀解惑到上海沙龍的微觀探討,再到云計算服務(wù)的具體賦能,智能制造轉(zhuǎn)型已進(jìn)入深化實踐階段。制造業(yè)、互聯(lián)網(wǎng)與IT的跨界融合,正以前所未有的力度重塑產(chǎn)業(yè)格局,推動中國制造向中國智造穩(wěn)步邁進(jìn)。

如若轉(zhuǎn)載,請注明出處:http://m.budbuds.cn/product/10.html

更新時間:2026-04-14 03:44:23